GSoC23 — Workweek 1

Introduction

The first workweek for my GSoC23 project is already over :D

Down below I will explain what I did this week, but first a disclaimer: I am currently not working at full capacity for GSoC, as I still have some obligations throughout June. This is why I opted for the extended timeline, therefore my work pace will definitely increase later on.

Work

My work during this week was to wade through the whole codebase of Icarus Verilog and try to understand the big picture.

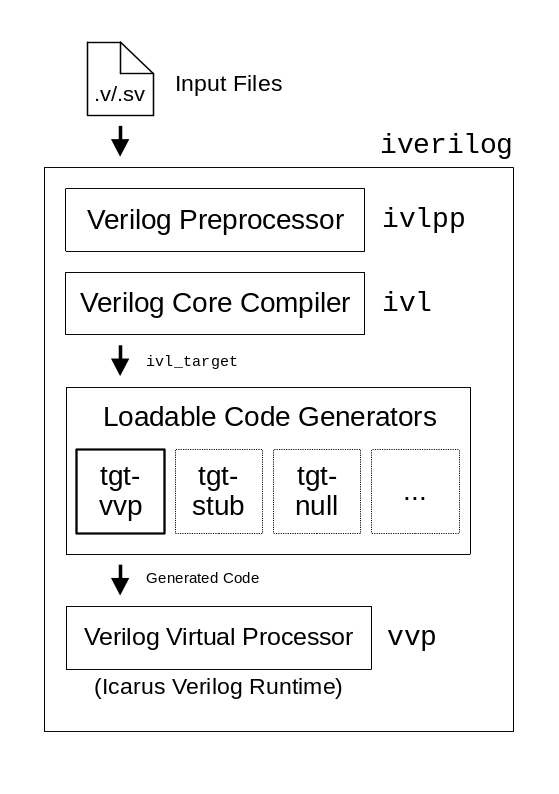

I have created this (big-)picture for you to explain how the Icarus Verilog Compilation System works:

As you can see, Icarus Verilog is much more than what it says on the box. And being a simulator is just one of its capabilities.

So let me explain:

-

First you start with your input files, for example

hello_world.vand pass them to iverilog like this:iverilog -o top.vvp -s top hello_world.vThe argument

-otells iverilog what name the output file should have,-stells it what the top-level module is, and finally we pass the input file(s).The contents of

hello_world.vare:module top; initial $display("Hello World!"); endmodule -

Next iverilog invokes the Verilog Preprocessor,

ivlpp. It does what a preprocessor does, such as replacing include directives with the content of the file, expanding macros, etc. -

Now follows the actual compiler,

ivl. It will read the preprocessed design, perform synthesis if desired and generate a netlist out of the design. -

One of the available code generators is chosen to receive the design netlist via the

ivl_targetAPI. Which code generator you say? We haven't chosen? Well, you are right, but if not explicately stateted, then iverilog will choose the default code generator,tgt-vvp.You can specify which code generator to use like this:

iverilog -o top.vvp -tvvp -s top hello_world.vWhere

-tvvpcan be any other available code generator, for example-tvlog95. See The Icarus Verilog Targets for more information.The

tgt-vvptarget will read the netlist and generate code, ready forvvp. -

Now we finally run the simulation by calling:

vvp top.vvpThis will print

Hello World!and terminate the simulation.VVP stands for Verilog Virtual Processor and is the simulation engine of Icarus Verilog. It will execute the code which was previously generated, which is the simulation of our simple "Hello World" design.

Trying to understand how Icarus Verilog works has certainly taken some time, but will hopefully help me implement the new features more efficiently - thus save me some time in the long run.

While trying to get the full big-picture, I updated the new documentation based on Sphinx with the information that I found. There are a lot of text documents all around the repository with important information. Therefore I have tried to unify all of this in the new documentation so that there is only one golden reference and you always know where to search for information.

You can find the associated PR here: #932.

Summary

This is all for this week. Next week I will try to finish up the PR and start to prepare detailed plans for the SDF INTERCONNECT feature.